**Noel M. Morris**

# ELEMENTI DI ELETTRONICA DIGITALE

Dispositivi semiconduttori e circuiti integrati - Porte logiche di base - I circuiti logici Porte logiche NAND e NOR - Elementi bistabili - La numerazione e l'aritmetica binaria - Circuiti contatori - Registri di scorrimento (shift register) Sistemi di memoria - Visualizzatori alfanumerici - Calcolatori e microprocessori - Attrezzature di collaudo

**HOEPLI**

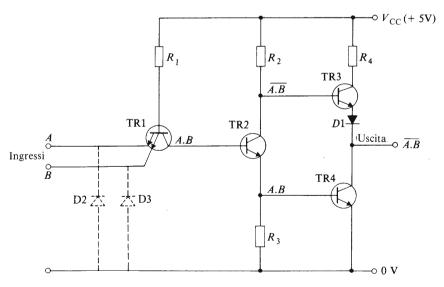

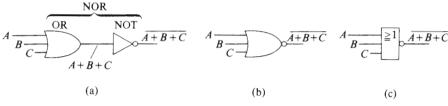

### **ENCICLOPEDIA HOEPLI**

in 14 volumi

completa e aggiornata

In-4 (22×28 cm) di pagine LXIV-7028 contenenti 72910 voci, 88140 accezioni, 10340 disegni originali al tratto, 1202 riproduzioni di capolavori d'arte in 145 tavole fuori testo in rotocalcografia e 856 soggetti e disegni a colori in 76 tavole fuori testo. L'opera completa e aggiornata (marzo 1979), rilegata in tutto skivertex, titoli e fregi in oro fino

ISBN 88-203-1124-0 L. 400.000

MORRIS N.M., Elementi di elettronica teorica e pratica. Traduzione di *P. Adorni.* In-8, di pagine XIV-302, con 199 figure. Copertina a colori plasticata e telata ISBN 88-203-1092-9 L. 8000

Circuiti a corrente continua - Resistori - Condensatori - Induttori - Tensioni e correnti alternate - Circuiti a corrente alternata sinusoidale - Trasformatori - Diodi a stato solido - Transistori - Optoelettronica - Amplificatori e circuiti logici fondamentali - Microeletronica e circuiti integrati - Amplificatori a retroazione e oscillatori - Amplificatori operazionali - Alimentatori stabilizzati e elettronica di potenza - Apparecchi di misura.

- BARANZINI R. e G. DUGNANI, **Microprocessori e microcomputers**. 2\* edizione riveduta e aggiornata. In-8, di pagine XIV-450, con 220 figure e 13 tabelle. Copertina a colori plasticata ISBN 88-203-1198-4 L. 22000

- CERRUTTI R. e M. MOROCUTTO, Introduzione ai microprocessori. Il codice binario - I circuiti logici - II microcomputer - La programmazione - I sistemi di sviluppo - Un esempio reale - Microprocessori in commercio -Glossario. In-8, di pagine VIII-112, con 33 figure e tabelle. Copertina a colori plasticata e telata ISBN 88-203-1172-0 L. 6000

COSTA E., Radioriparatore:

Volume I: "Audio radio". 10<sup>a</sup> edizione completamente rifatta. In-8, di pagine XII-368, con 486 figure. Copertina a colori plasticata e telata ISBN 88-203-0961-0 L. 12000

Volume II: "Componenti-Misure-Allineamenti-Guasti". 10<sup>a</sup> edizione completamente rifatta. In-8, di pagine XII-268, con 323 figure. Copertina a colori plasticata. ISBN 88-203-1167-4 L. 15000

- GHERSEL F., I cinescopi a colori. Cinescopi ad un fascio Cinescopi a tre fasci a delta Cinescopi a tre fasci allineati Fosfori Funzionamento Fabbricazione Circuiti associati Difetti Misure Definizioni Nomenclatura in italiano, inglese, francese, tedesco. In-8, di pagine X-182, con 126 figure in bianco e nero e a colori e 7 tabelle. Copertina a colori plasticata e telata

ISBN 88-203-1160-7 L. 15000

- Schemario TVC. Servizio, misure e schemi di televisori a colori. In-4, di pagine X-214, con 150 figure in bianco e nero e a colori. Copertina a colori plasticata ISBN 88-202-1213-1 L. 22000

- GRIFFIN G. e P. SAPORITO, Videotape. Guida all'uso dei mezzi televisivi leggeri. IN-8, di pagine VIII-216, con 97 illustrazioni di Gabriel Griffin. Copertina a colori plasticata

ISBN 88-203-1187-9

L. 12000

- MENDOLIA I., Elettronica generale, ad uso degli Istituti tecnici industriali.

In-8, di pagine XVI-832, con 862 figure e 5 tavole. Copertina a colori plasticata

ISBN 88-203-1171-2 L. 20000

- MIOTTO M., II televisore a colori PAL. Circuiti a transistori e integrati -Sovraimpressioni - Giochi al televisore. In-8, di pagine XII-148, con 161 figure, 4 tabelle. Copertina a colori plasticata e telata ISBN 88-202-1136-4 L. 10000

- POTENZA F., La matematica per il calcolatore tascabile. Problemi di lavoro, grafici, giochi, impostati e risolti col minicalcolatore. In-16, di pagine X-294, con 27 figure. Copertina a colori plasticata e telata

- ISBN 88-203-1059-7 L. 4500

RAVALICO D.E., II radiolibro. Radiotecnica pratica. 19\* edizione ampliata e

aggiornata a cura di Giorgio Terenzi. In-8, di pagine VIII-500, con 108 figure, 628 zoccoli e valvole di transistore di I.C., 65 tabelle e 5 tavole fuori testo. Copertina a colori plasticata e telata ISBN 88-203-1044-9 L. 10000

#### EDITORE ULRICO HOEPLI MILANO

## ELEMENTI DI ELETTRONICA DIGITALE

## ELEMENTI DI ELETTRONICA DIGITALE

Dispositivi semiconduttori e circuiti integrati - Porte logiche di base I circuiti logici - Porte logiche NAND e NOR Elementi bistabili - La numerazione e l'aritmetica binaria Circuiti contatori - Registri di scorrimento (shift register) Sistemi di memoria - Visualizzatori alfanumerici Calcolatori e microprocessori - Attrezzature di collaudo

EDITORE ULRICO HOEPLI MILANO

Titolo dell'edizione originale inglese:

Digital Electronics for Works Electricians

Copyright © 1979 McGraw-Hill Book Company (UK) Limited.

All rights reserved.

Traduzione di Maria Rimini

Per l'edizione italiana:

Copyright © Ulrico Hoepli Editore S.p.A. 1981 via Hoepli 5, 20121 Milano (Italy)

Tutti i diritti sono riservati a norma di legge e a norma delle convenzioni internazionali

ISBN 88-203-1243-3

Composto e impresso dalla Lito Velox Trento - via Orbi, 6

Printed in Italy

## Indice generale

## Capitolo 1 **Dispositivi semiconduttori e circuiti integrati**

| 1.1  | Elettroni e buche                             | 1  |

|------|-----------------------------------------------|----|

| 1.2  | Semiconduttori                                | 3  |

| 1.3  | Caratteristiche dei diodi                     | 4  |

| 1.4  | Diodi semiconduttori a giunzione p-n          | 6  |

| 1.5  | I diodi Zener                                 | 8  |

| 1.6  | Tempo di immagazzinamento nei diodi           | 9  |

| 1.7  | Diodi a barriera Schottky                     | 9  |

| 1.8  | Transistori bipolari a giunzione              | 10 |

| 1.9  | Transistori a effetto di campo (FET)          | 13 |

| 1.10 | I MOSFET                                      | 13 |

| 1.11 | Precauzioni nel maneggiare i MOSFET           | 16 |

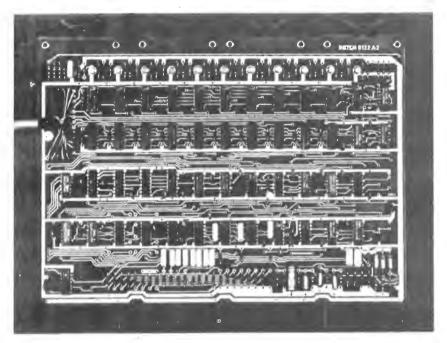

| 1.12 | Circuiti integrati monolitici (IC)            | 17 |

| 1.13 | Costruzione di un circuito integrato bipolare | 18 |

| 1.14 | Costruzione dei circuiti integrati MOS        | 22 |

| 1.15 | Impaccamento di circuiti integrati            | 22 |

| 1.16 | Circuiti MSI e LSI                            | 23 |

|      |                                               |    |

|      |                                               |    |

|      | Capitolo 2                                    |    |

|      | Porte logiche di base                         |    |

| 2.1  | Porte logiche                                 | 24 |

| 2.2  | Livelli di segnali logici                     | 25 |

| 2.3  | Un problema logico                            | 25 |

| 2.4  | La porta NOT                                  | 26 |

| 2.5  | La porta OR                                   | 28 |

| 2.6  | La porta AND                                  | 30 |

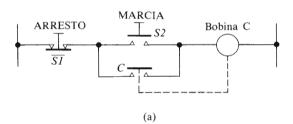

| 2.0  | Il circuito completo di controllo             | 21 |

| 2.8<br>2.9   | Stesura di tabelle della verità                                                                          | 32 |  |  |

|--------------|----------------------------------------------------------------------------------------------------------|----|--|--|

|              | te logiche                                                                                               | 34 |  |  |

|              | Capitolo 3                                                                                               |    |  |  |

|              | I circuiti logici                                                                                        |    |  |  |

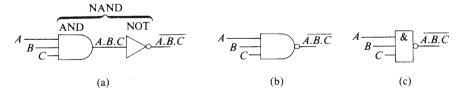

| 3.1          | Una porta logica OR a diodo resistore (DRL)                                                              | 36 |  |  |

| 3.2          | Fan-in e fan-out                                                                                         | 38 |  |  |

| 3.3<br>3.4   | Una porta logica AND a diodo resistore                                                                   | 39 |  |  |

|              | corrente                                                                                                 | 40 |  |  |

| 3.5          | Il rumore nei sistemi logici                                                                             | 41 |  |  |

| 3.6          | Il transistore come interruttore - la porta NOT                                                          | 43 |  |  |

| 3.7          | Le porte logiche NOT a MOS                                                                               | 44 |  |  |

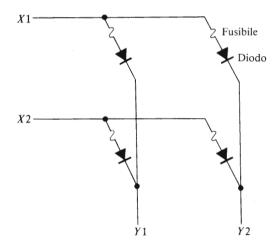

| 3.8          | La conversione di un circuito a relè in forma logica                                                     | 45 |  |  |

| 3.9          | Ulteriori proprietà richieste per un sistema logico                                                      | 48 |  |  |

|              | Capitolo 4  Porte logiche NAND e NOR                                                                     |    |  |  |

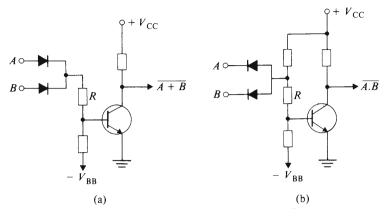

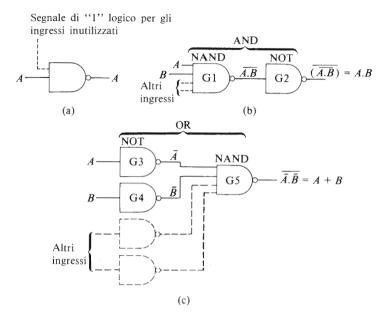

| 4.1          | La ragione dell'esistenza di porte NAND e NOR                                                            | 49 |  |  |

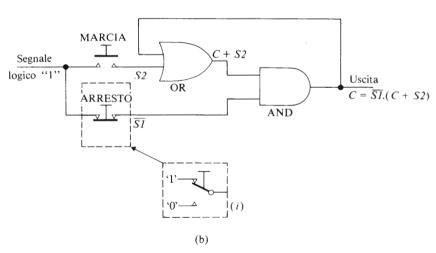

| 4.2          | Il principio della porta NAND                                                                            | 49 |  |  |

| 4.3          | Circuiti tipici contenenti la porta NAND                                                                 | 50 |  |  |

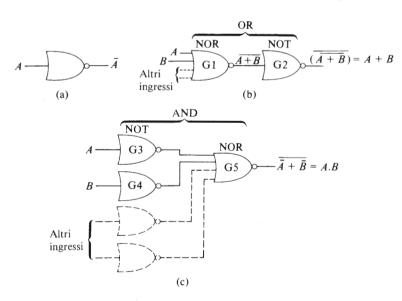

| 4.4          | Il principio della porta NOR                                                                             | 54 |  |  |

| 4.5          | Circuiti tipici contenenti la porta NOR                                                                  | 55 |  |  |

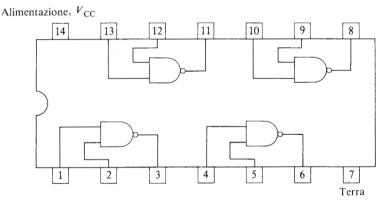

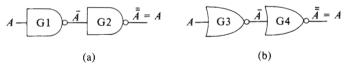

| 4.6          | Utilizzo delle porte NAND                                                                                | 55 |  |  |

| 4.7          | Utilizzo delle porte NOR                                                                                 | 58 |  |  |

| 4.8          | Un semplice metodo di minimizzazione                                                                     | 60 |  |  |

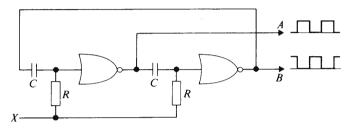

| 4.9          | Un oscillatore a onde quadre                                                                             | 61 |  |  |

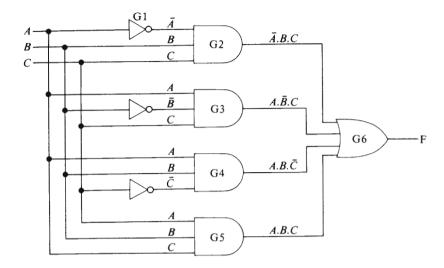

| 4.10         | Introduzione al progetto di reti logiche (sintesi di reti)                                               | 61 |  |  |

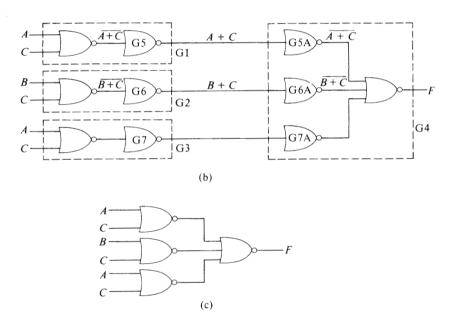

| 4.11<br>4.12 | Il minimizzare il circuito elettronico di voto<br>La trasformazione di una rete AND, OR, NOT in una rete | 64 |  |  |

| 7.12         | NAND                                                                                                     | 66 |  |  |

| 4.13         | La conversione di una rete AND, OR, NOT in una rete NOR                                                  | 67 |  |  |

|              |                                                                                                          |    |  |  |

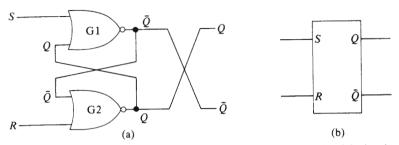

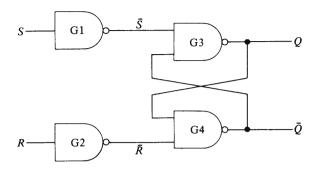

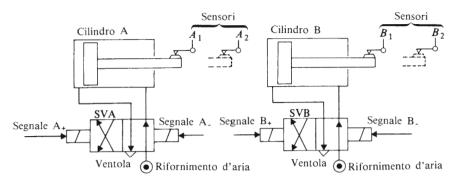

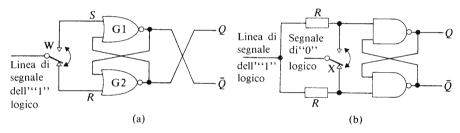

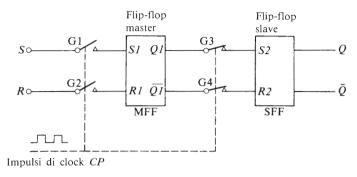

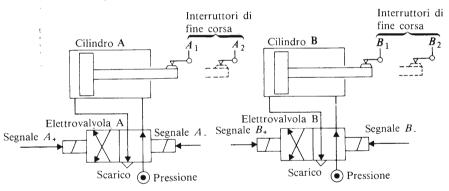

### Elementi bistabili

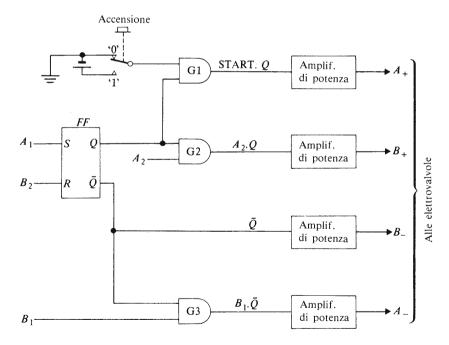

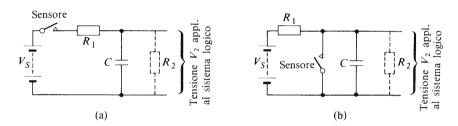

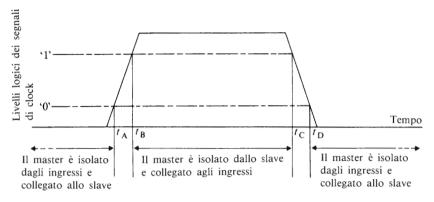

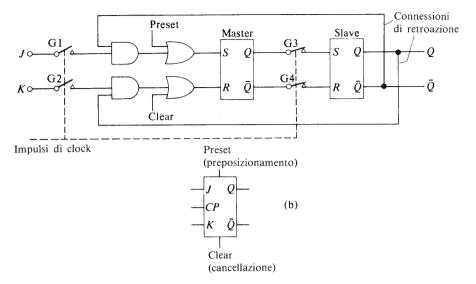

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7 | Che cos'è un elemento bistabile?  Il flip-flop set-reset (S-R)  Sequenza di controllo di pistoni contenenti un flip-flop S-R.  Eliminatori dei rimbalzi di contatto  Flip-flop master-slave  Il flip-flop S-R master-slave  Il flip-flop master-slave J-K | 70<br>70<br>73<br>76<br>78<br>78 |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

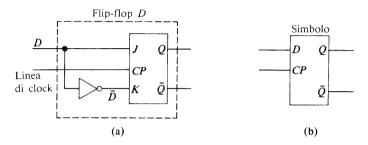

| 5.8<br>5.9                                    | Il flip-flop master-slave D                                                                                                                                                                                                                               | 81<br>83<br>85                   |

|                                               | Capitolo 6 <b>Numerazione e aritmetica binaria</b>                                                                                                                                                                                                        |                                  |

| 6.1                                           | Sistemi di numerazione                                                                                                                                                                                                                                    | 86                               |

| 6.2                                           | Immagazzinamento di numeri frazionari                                                                                                                                                                                                                     | 88                               |

| 6.3                                           | La lunghezza delle "parole" (words) binarie                                                                                                                                                                                                               | 88                               |

| 6.4                                           | Codici decimali codificati in binario (BCD)                                                                                                                                                                                                               | 89                               |

| 6.5<br>6.6                                    | Codici alfanumerici                                                                                                                                                                                                                                       | 91                               |

| 0.0                                           | rità (parity checks)                                                                                                                                                                                                                                      | 92                               |

| 6.7                                           | Codici sensibili alla posizione                                                                                                                                                                                                                           | 94                               |

| 6.8                                           | Addizione binaria                                                                                                                                                                                                                                         | 96                               |

| 6.9                                           | Sottrazione binaria                                                                                                                                                                                                                                       | 99                               |

| 6.10                                          | Moltiplicazione                                                                                                                                                                                                                                           | 101                              |

| 6.11                                          | Divisione                                                                                                                                                                                                                                                 | 102                              |

|                                               | Capitolo 7                                                                                                                                                                                                                                                |                                  |

|                                               | Circuiti contatori                                                                                                                                                                                                                                        |                                  |

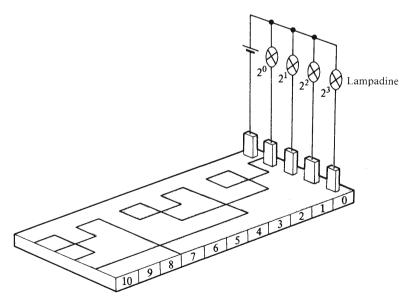

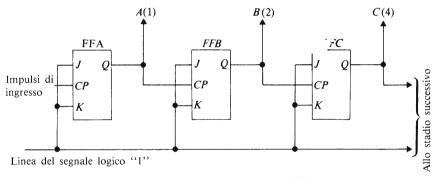

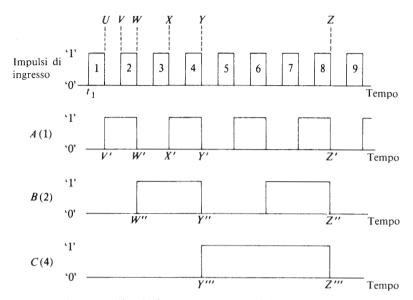

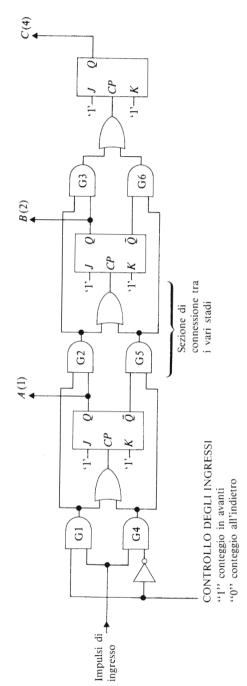

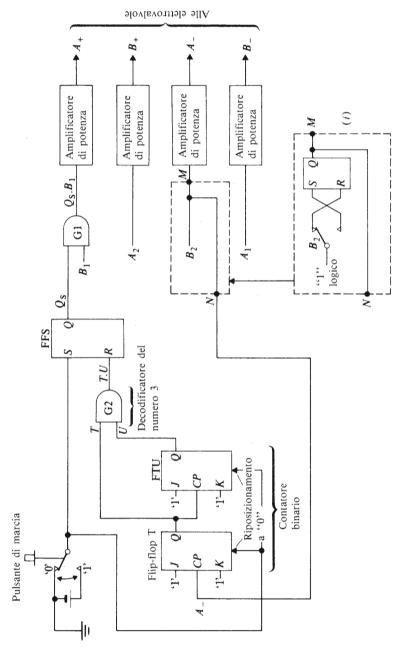

| 7.1<br>7.2<br>7.3<br>7.4<br>7.5               | A che velocità?                                                                                                                                                                                                                                           | 103<br>104<br>107<br>108<br>110  |

| 7.6<br>7.7   | Circuiti di conteggio integrati                               | 112<br>114 |

|--------------|---------------------------------------------------------------|------------|

| 7.7          | Sequenza di controllo dei pistoni, 3 cicli                    | 121        |

|              |                                                               |            |

|              | Capitolo 8                                                    |            |

|              | Registri di scorrimento (shift register)                      |            |

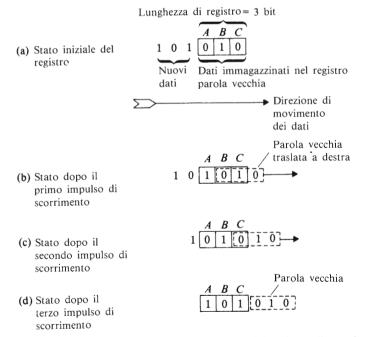

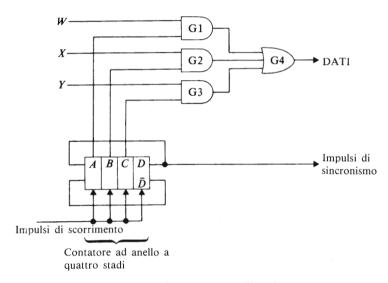

| 8.1          | Cos'è un registro di scorrimento?                             | 125        |

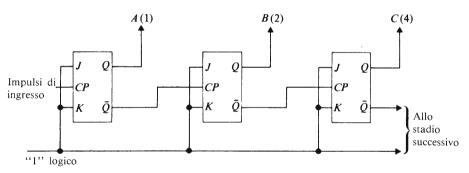

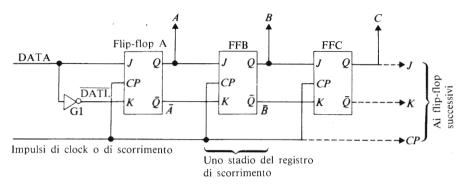

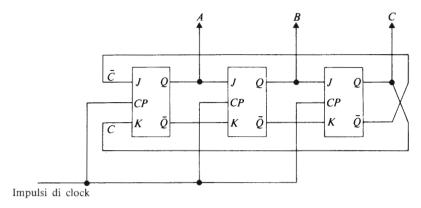

| 8.2          | Un registro di scorrimento che utilizza i flip-flop $J$ - $K$ | 126        |

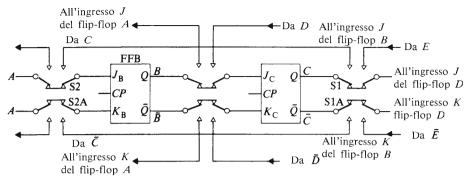

| 8.3          | Un registro di scorrimento reversibile                        | 128        |

| 8.4          | Applicazioni industriali dei registri di scorrimento          | 129        |

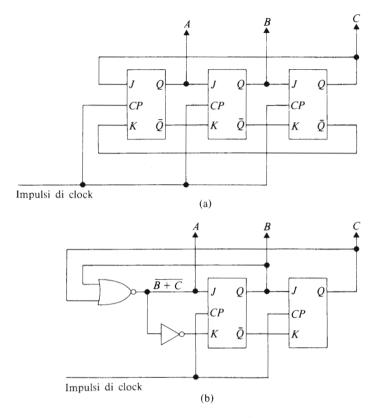

| 8.5<br>8.6   | Un contatore ad anello (ring counter)                         | 130        |

|              | contatore a anello                                            | 132        |

| 8.7          | Contatore a codice Johnson o "twisted-ring counter"           | 134        |

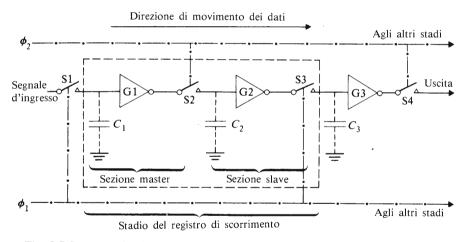

| 8.8          | Un registro di scorrimento dinamico a MOSFET                  | 136        |

|              |                                                               |            |

|              | Capitolo 9                                                    |            |

|              | Sistemi di memoria                                            |            |

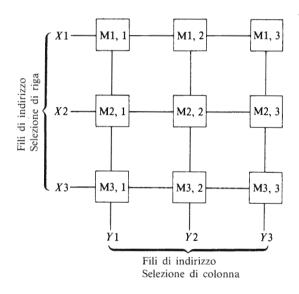

| 9.1          | Tipi di elementi di memoria                                   | 138        |

| 9.2          | Memorie ad accesso casuale (RAM)                              | 138        |

| 9.3          | Memorie di sola lettura                                       | 140        |

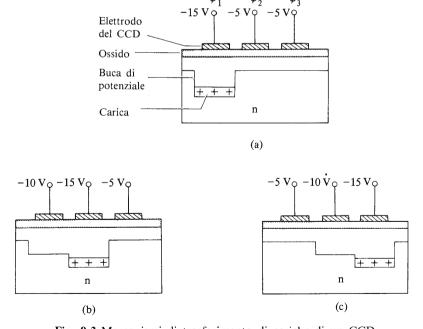

| 9.4          | Dispositivi ad accoppiamento di carica                        | 142        |

|              |                                                               |            |

|              | Capitolo 10                                                   |            |

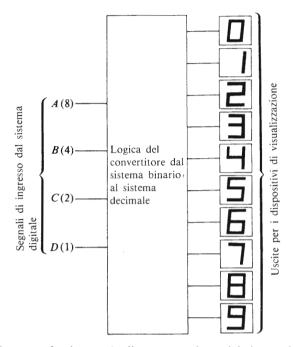

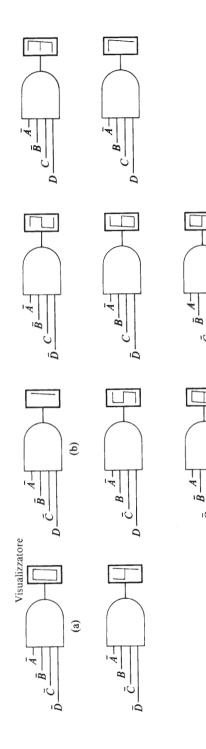

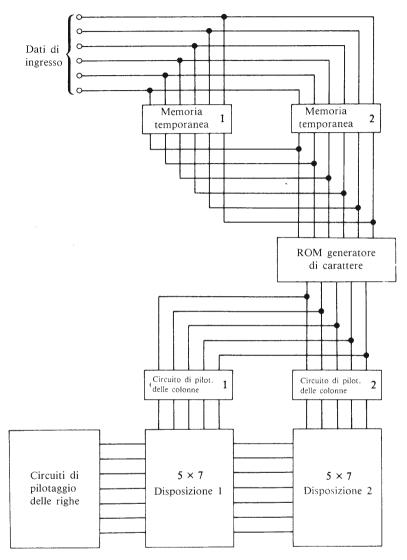

|              | Visualizzatori alfanumerici                                   |            |

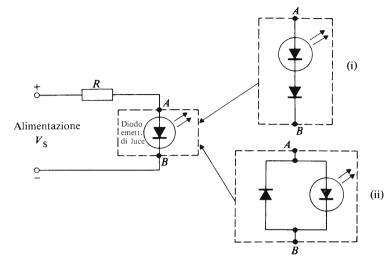

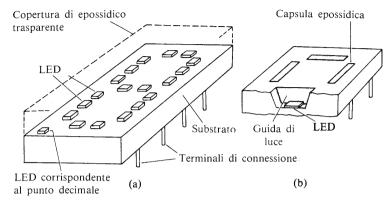

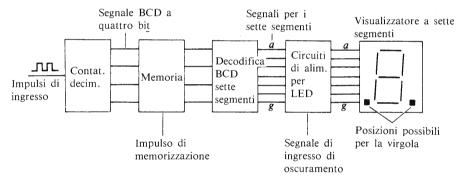

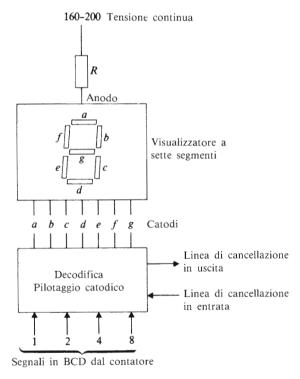

| 10.1         | Diodi emettitori di luce                                      | 144        |

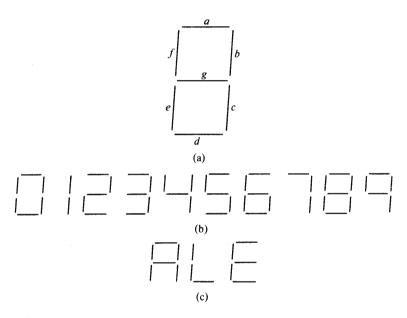

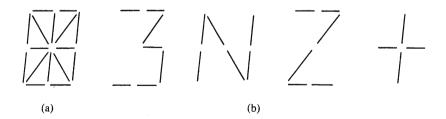

| 10.2         | Visualizzatori a LED a segmenti                               | 146        |

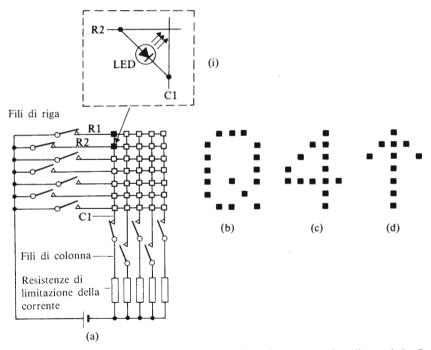

| 10.3         | Visualizzatori a diodi LED a punti (dot array led displays) . | 149        |

| 10.4         | Visualizzatori a LED multipli                                 | 150        |

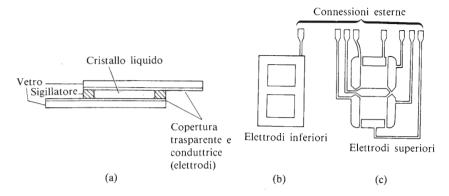

| 10.5         | Visualizzatori a cristalli liquidi                            | 150        |

| 10.6         | Visualizzatori a scarica nei gas                              | 153        |

| 10.7<br>10.8 | Visualizzatori a filamenti                                    | 155        |

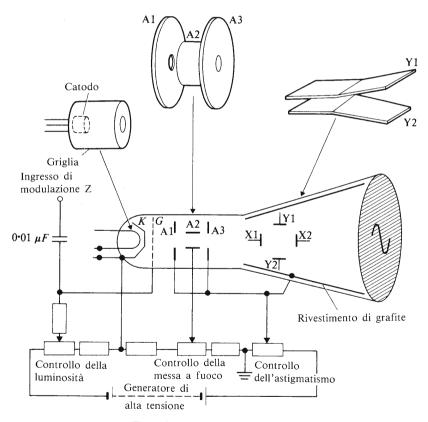

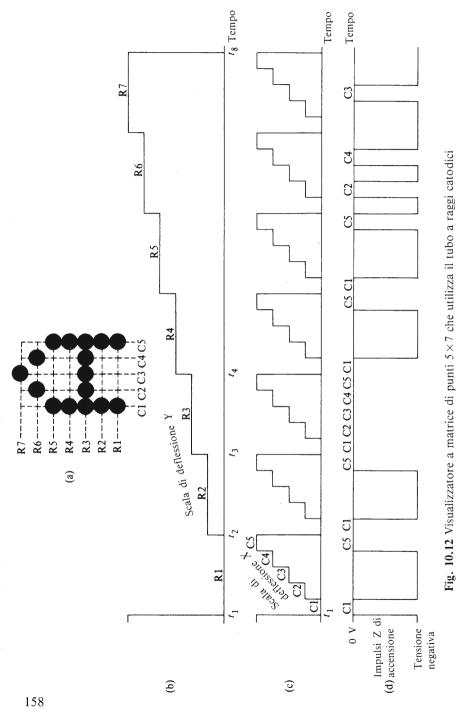

| 10.8         | Visualizzatori a tubi a raggi catodici                        | 155<br>155 |

| 10.9         | risuanizzatori a tuoi a raggi catouici                        | 133        |

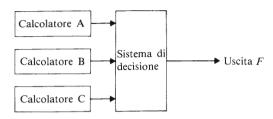

## Calcolatori e microprocessori

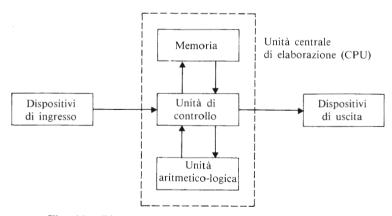

| 11.1                     | Cos'è un calcolatore digitale?                           | 160 |  |  |

|--------------------------|----------------------------------------------------------|-----|--|--|

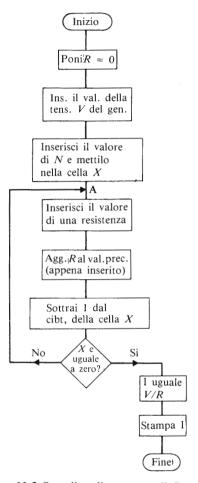

| 11.2                     | Diagrammi di flusso                                      | 163 |  |  |

|                          | I linguaggi di programmazione                            | 165 |  |  |

|                          | Microprocessori e microcalcolatori                       | 168 |  |  |

|                          | Controllo della sequenza di movimento di due pistoni per |     |  |  |

|                          | mezzo di un microprocessore                              | 173 |  |  |

|                          | Capitolo 12                                              |     |  |  |

| Attrezzature di collaudo |                                                          |     |  |  |

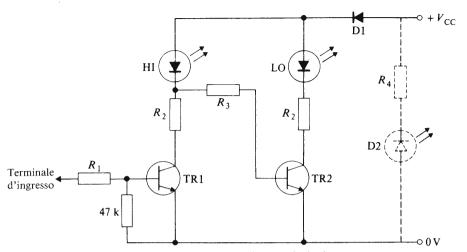

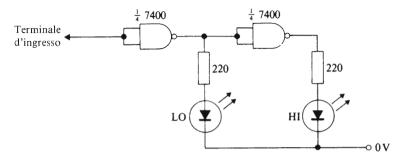

|                          | Ricerca dei guasti nei circuiti digitali                 | 178 |  |  |

| 12.2                     | Sonde e "pinze" logiche                                  | 178 |  |  |

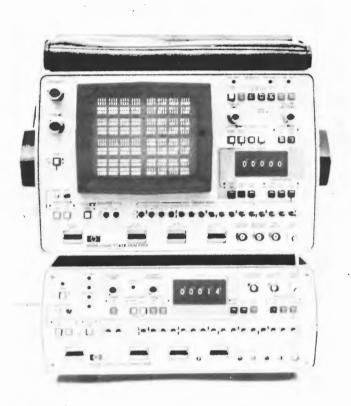

| 12.3                     | Analizzatori di stati logici                             | 182 |  |  |

|                          | Strumenti di misura analogici                            | 183 |  |  |

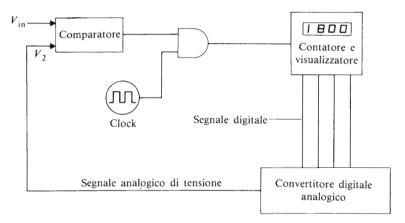

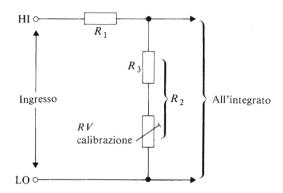

|                          | Voltmetri digitali (D.V.M)                               | 184 |  |  |

| 12.6                     | Multimetri digitali                                      | 186 |  |  |

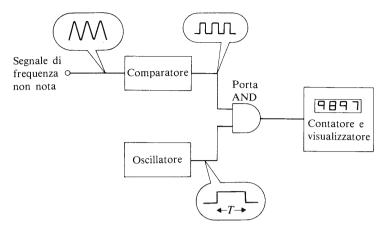

|                          | Misura digitale della frequenza                          | 188 |  |  |

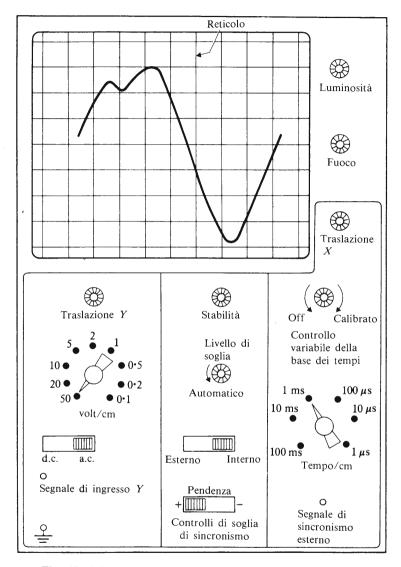

|                          | L'oscilloscopio a raggi catodici                         | 189 |  |  |

# Dispositivi semiconduttori e circuiti integrati

#### 1.1 Elettroni e buche

Una corrente elettrica è spiegabile in termini di movimento di *cariche* elettriche tra due punti distinti di un circuito. Per spiegare il flusso di corrente è necessario sapere qualcosa sulla struttura atomica dei materiali usati nei circuiti elettronici.

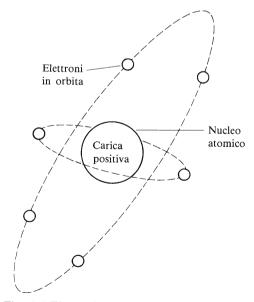

Da un punto di vista ingegneristico, un atomo consiste di due tipi di particelle cariche, **elettroni** e **protoni**. La massa del protone è 1840 volte quella dell'elettrone; i protoni sono concentrati al centro dell'atomo, detto *nucleo*, come in Fig. 1.1. Un protone porta una carica elettrica po-

Fig. 1.1 Elettroni in orbita attorno al nucleo

sitiva, mentre l'elettrone ne porta una uguale ed opposta. Ogni atomo ha tanti elettroni quanti protoni, cosicché la carica elettrica complessiva è nulla. Se un atomo perdesse un elettrone, resterebbe con una carica positiva in eccesso.

Gli elettroni orbitano attorno al nucleo (Fig. 1.1) in quelle che sono definite **bande**, **strati** o **gusci**. Si può tracciare una semplice analogia tra gli strati degli elettroni e i livelli di parcheggio per auto in un posteggio a molti piani. Il piano terra può essere considerato come il nucleo dell'atomo, mentre i piani superiori rappresentano i livelli di energia in cui si possono trovare gli elettroni. In natura, i livelli d'energia più bassi dell'atomo devono essere pieni di elettroni prima che altri elettroni possano comparire nei livelli a contenuto d'energia superiore (nel caso del parcheggio, sono i piani inferiori ad essere riempiti per primi).

Quando un livello energetico è completo, si raggiunge una configurazione elettronica di grande stabilità, per cui non sono possibili, senza un elevato dispendio di energia, movimenti di elettroni al di fuori dell'orbita atomica corrispondente a ciascuno di essi. Tuttavia è probabile che i livelli energetici più elevati in cui si trovano gli elettroni, non siano completamente pieni. Il guscio più esterno dell'atomo che contiene almeno un elettrone è detto banda di valenza o livello energetico di valenza; gli elettroni che in definitiva prendono parte al processo di conduzione orbitano nella banda di valenza.

Perché un elettrone possa prendere parte alla conduzione, deve acquistare una quantità di energia superiore a quella necessaria a mantenerlo orbitante nella banda di valenza. L'energia può venire fornita da molte sorgenti, compresi il calore, la luce e le radiazioni atomiche. L'applicazione di una tensione elettrica a un semiconduttore dà come risultato l'applicazione di una forza elettrica agli elettroni della banda di conduzione, forza che li si spinge verso il polo positivo del generatore. Gli elettroni che arrivano al polo positivo costituiscono il flusso di corrente nel circuito, contemporaneamente un numero uguale di elettroni viene immesso nel circuito da parte del polo negativo della batteria per mantenere bilanciata la carica elettronica all'interno del semiconduttore.

Quando un elettrone sfugge a un atomo, diventa una carica elettrica negativa *mobile*; dato che l'atomo ha perso un elettrone (una carica negativa, cioè), rimane con una carica positiva netta corrispondente a un'unità di carica elettrica. Come risultato di questo, cercherà di attrarre a sé un elettrone mobile che si trovi nelle sue vicinanze. Perciò è possibile descrivere la carica positiva sull'atomo come una **buca** elettronica; una buca può essere considerata un portatore di carica positiva, così co-

me un elettrone è un portatore di carica negativa. Una buca è semplicemente l'assenza di un elettrone da un punto della struttura dove normalmente se ne dovrebbe trovare uno.

#### 1.2 Semiconduttori

Un semiconduttore è un materiale la cui resistività è compresa tra quella di un buon conduttore e quella di un buon isolante. I materiali semiconduttori comunemente usati nei diodi e nei transistori sono il silicio e il germanio, mentre altri materiali come l'arseniuro di gallio e il fosfuro di gallio sono utilizzati in altri dispositivi come i diodi fotoemettitori (LED). Il silicio è l'elemento semiconduttore di gran lunga più usato e si trova in molti tipi di rocce e pietre (ad esempio, la sabbia è biossido di silicio).

Il passaggio di corrente in un semiconduttore puro è il risultato di movimenti di elettroni e buche generati principalmente dagli effetti termici come delineato nel paragrafo 1.1. All'aumentare della temperatura esterna, aumenta il numero di elettroni che possono prendere parte al fenomeno di conduzione. Quindi, per un determinato valore della tensione applicata, l'intensità di corrente attraverso un materiale semiconduttore aumenta con la temperatura, cioè la sua resistenza diminuisce con l'aumentare della temperatura. In altre parole, la resistività nei semiconduttori presenta un coefficiente termico negativo. Il flusso di corrente creato da questo effetto è, nel caso dei diodi e dei transistori, un inconveniente poiché dà origine a una corrente di perdita che dipende dalla temperatura. I dispositivi al germanio hanno un valore della corrente di perdita dovuta a questo effetto superiore rispetto a quelli al silicio. Questo tipo di conduttività è detto conduttività intrinseca; e per questa ragione, i semiconduttori puri sono detti semiconduttori di tipo i.

Per ottenere un valore di conduttività che possa essere controllato dall'esterno, si introducono nel semiconduttore, durante il processo di fabbricazione, quantità definite di impurità. La quantità tipica introdotta è di 1 parte ogni 10 milioni di parti di materiale puro. Secondo il tipo di impurità aggiunta il semiconduttore è detto tipo n o di tipo p.

In un materiale di **tipo p**, le impurità aggiunte provocano un eccesso di buche mobili. La dizione "di tipo p" implica che ci siano portatori di cariche **p**ositive. Il gallio e l'iridio sono materiali spesso usati nel drogaggio del silicio per produrre un semiconduttore di tipo p. Ricordiamo che in un pezzo isolato di materiale di tipo p ci sono un egual numero di elettroni e di buche, cosicché, considerandolo nel suo insieme, esso è

elettricamente neutro; tuttavia, non tutti i portatori di carica sono "liberi" di dar luogo a un flusso di corrente, dato che la maggior parte di essi è legata agli atomi da forze elettrostatiche di legame atomico. Così, la corrente in un materiale di tipo p è in gran parte dovuta al movimento di portatori mobili di cariche positive verso il polo negativo del generatore. Perciò nei semiconduttori di tipo p, i buchi sono chiamati portatori di maggioranza. Contemporaneamente per effetto termico viene generato un numero assai esiguo di elettroni mobili i quali danno un piccolo contributo all'intensità della corrente. In un materiale di tipo p gli elettroni sono perciò detti portatori di minoranza.

In un materiale di **tipo n**, la droga usata (solitamente arsenico o antimonio) provoca un eccesso di elettroni mobili (la dizione "di tipo n" implica che ci siano portatori di carica **n**egativa). Nei materiali di tipo n, la maggior parte dell'intensità di corrente è dovuta a movimenti di elettroni attraverso il materiale, e in *questo caso gli elettroni sono chiamati portatori di maggioranza*.

I movimenti delle buche (che sono i *portatori di minoranza in materiali di tipo n*), generate da effetti termici, danno anch'essi un piccolo contributo all'intensità di corrente.

Entrambi i semiconduttori di tipo p e di tipo n sono utilizzati nella fabbricazione dei dispositivi semiconduttori. Alcuni dispositivi particolari usano invece semiconduttori di tipo i.

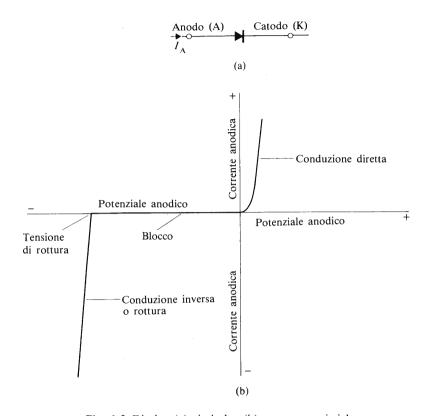

#### 1.3 Caratteristiche dei diodi

Un diodo è un dispositivo elettronico con due terminali (elettrodi) uno dei quali è detto **anodo** e l'altro **catodo** (Fig. 1.2a). Il diodo presenta una bassa resistenza al passaggio di corrente quando il potenziale anodico è positivo rispetto a quello catodico, e in questo caso si dice che è **polarizzato direttamente**. Quando, invece, il potenziale anodico è negativo rispetto a quello catodico, il diodo presenta una resistenza molto elevata al passaggio di corrente, e in questo caso si dice che esso è **polarizzato inversamente**. In tale senso il diodo può essere considerato come un **interruttore sensibile alla tensione**, che è chiuso quando è polarizzato direttamente e aperto quando è polarizzato inversamente.

In un diodo semiconduttore (vedi paragrafo 1.4) il catodo è generalmente contrassegnato con un punto o con una striscia colorata. I diodi possono essere provati usando un tester in funzione di ohmmetro. Bisogna notare che il terminale "+" di uno strumento del genere è in realtà negativo rispetto al terminale "-" per il fatto di essere collegato

Fig. 1.2 Diodo: (a) simbolo; (b) sue caratteristiche

con una batteria interna (vedi per i dettagli: Noel M. Morris, *Elementi di elettronica teorica e pratica*, Hoepli). Quando l'anodo di un diodo efficiente è collegato al terminale "—" dello strumento e il catodo al terminale "+", la resistenza indicata dallo strumento dovrebbe essere bassa; quando i collegamenti sono scambiati lo strumento dovrebbe indicare una resistenza infinita.

Quando il diodo è polarizzato direttamente (Fig. 1.2b), la caduta di tensione diretta attraverso di esso varia generalmente da 0,2 a 0,6 V per un diodo al germanio e da 0,5 a 0,8 V per un diodo al silicio.

Quando il diodo è polarizzato inversamente con una tensione applicata inferiore alla tensione di rottura, si dice che funziona da **blocco**; in questo stato operativo soltanto la **corrente di perdita** fluisce attraverso il diodo. Nei diodi normalmente usati nei circuiti logici, il valore della corrente di perdita è di solito di alcuni nanoampere (1 nA =  $10^{-9}$ A); per le ragioni già viste la corrente di perdita aumenta leggermente con l'aumentare della temperatura.

Esiste un valore della tensione inversa noto come **tensione di rottura** (Fig. 1.2 b) al di là del quale la corrente in senso inverso aumenta rapidamente; a tensioni più elevate della tensione di rottura si dice che il diodo è in **conduzione inversa**. Nel caso di diodi usati nei circuiti logici e nei raddrizzatori, questo stato provoca un aumento della dispersione di potenza al loro interno che può raggiungere livelli pericolosamente alti e danneggiare perciò i diodi stessi. Diodi speciali noti come diodi Zener (vedi paragrafo 1.5) sono progettati per funzionare in conduzione inversa.

#### 1.4 Diodi semiconduttori a giunzione p-n

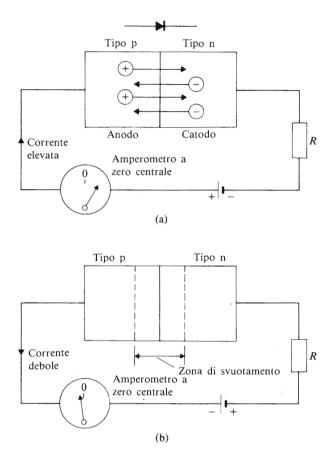

Il diodo a giunzione p-n è costituito da un monocristallo di materiale semiconduttore contenente una regione anodica di tipo p e una regione catodica di tipo n (Fig. 1.3).

Quando un diodo è collegato come in Fig. 1.3(a), con l'anodo di tipo positivo rispetto al catodo di tipo n (cioè è polarizzato direttamente), si rileva un elevato passaggio di corrente nel circuito. La ragione è la seguente: in un materiale di tipo p i portatori di maggioranza sono buche e in materiali di tipo n sono elettroni.

Quando la regione p è collegata al polo positivo del generatore, questo inietta nell'anodo le buche mobili le quali sono attratte verso la regione n dal polo negativo del generatore. Nello stesso tempo, la regione n riceve nuovi elettroni dal polo negativo e queste cariche mobili sono attratte nella regione p dal polo positivo del generatore stesso. Il flusso di questi portatori di carica costituisce il flusso di corrente nel circuito. Da quanto precede risulta che il diodo è polarizzato direttamente quando l'anodo di tipo p è positivo rispetto al catodo di tipo n.

Se la polarità è invertita come in Fig. 1.3(b), la corrente nel circuito diventa praticamente nulla (rimane solo la corrente di perdita). In questo caso (polarizzazione inversa) il potenziale negativo applicato all'anodo di tipo p attrae le buche mobili (portatori di carica positiva) e le allontana dalla giunzione p-n. Nello stesso tempo, il potenziale positivo applicato al catodo di tipo n attrae gli elettroni mobili allontanandoli dalla giunzione p-n.

Il risultato complessivo è che non rimangono portatori mobili nella zona di giunzione p-n; cioè la zona attorno alla giunzione è privata dei

**Fig. 1.3** Diodo a giunzione p-n polarizzato direttamente (a) e polarizzato inversamente (b)

portatori di carica ed è nota come **zona di svuotamento**. Dato che la zona di svuotamento non contiene portatori di carica liberi, diventa a tutti gli effetti uno strato isolante che impedisce ogni flusso di corrente attraverso il diodo, con l'eccezione della corrente di perdita. Nel caso di raddrizzatori, la rottura inversa del diodo avviene quando la tensione di polarizzazione inversa è sufficientemente elevata da rompere la zona di svuotamento. Nei diodi Zener (vedi paragrafo 1.5) la rottura inversa si ha invece per valori di tensione abbastanza piccoli.

#### 1.5 I diodi Zener

Un diodo Zener è un diodo a giunzione p-n il cui drogaggio è molto più elevato di quello di un diodo normale, il che determina una rottura inversa per piccoli valori di tensione (si possono costruire diodi Zener con tensioni di rottura tra qualche volt e poche centinaia di volt). Per ogni singolo dispositivo, la tensione di rottura ha un valore stabile ragionevolmente costante in un campo abbastanza ampio di valori di corrente inversa.

I diodi Zener sono quasi sempre usati in polarizzazione inversa, con l'anodo collegato al polo negativo del generatore. Per ogni dispositivo Zener è definibile un valore di dissipazione massima di potenza. Facendo riferimento alla relazione

$$I = \frac{\text{dissipazione di potenza}}{\text{tensione di rottura}}$$

la I indicata è la massima corrente inversa che può circolare senza danneggiare il dispositivo. Per esempio, un diodo Zener da 4 V, 1 W, può sopportare una corrente inversa I=1/4=0,25 A. Questi diodi trovano comune applicazione nei circuiti elettronici come sorgente di tensione di riferimento costante. Per questo tipo di applicazione, le pile campione sono state largamente soppiantate dai circuiti a diodi Zener.

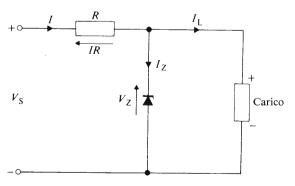

Una semplice sorgente di riferimento è mostrata in Fig. 1.4. Abbiamo una tensione  $V_S$  non stabilizzata, fornita da un ponte di raddrizzamento e da un circuito di filtro. Il valore di  $V_S$  è generalmente il doppio del valore della tensione di rottura ( $V_Z$ ) del diodo Zener. Il simbolo di diodo Zener è caratterizzato dal catodo piegato ad angolo (che simboleggia

Fig. 1.4 Stabilizzatore di tensione con diodo Zener

l'effetto di rottura). Il resistore R assolve la doppia funzione di limitare la corrente e di determinare una caduta di tensione. La differenza dei potenziali  $V_S$  e  $V_Z$  appare ai capi di R. Dato che il potenziale di rottura di un diodo Zener è praticamente costante, la tensione ai capi del carico è pure costante, malgrado le variazioni della tensione fornita dal generatore; le variazioni di  $V_S$  appaiono solo ai capi di R e non ai capi del diodo Zener.

#### 1.6 Tempo di immagazzinamento nei diodi

Per interdire un diodo a giunzione p-n che sta conducendo, è necessario prima eliminare tutte le cariche mobili nella regione della giunzione p-n. Solo dopo aver fatto questo, si può costruire nella zona della giunzione p-n la regione isolante di svuotamento. Il tempo perché questo si verifichi è detto *tempo di immagazzinamento* del dispositivo: esso, per i diodi usati in circuiti logici può variare da una frazione di nanosecondo (1ns = 10<sup>-9</sup> s) a un millisecondo (1ms = 10<sup>-3</sup> s) in un diodo ad alta corrente. Sebbene gli intervalli di tempo riportati siano piccoli, il tempo di immagazzinamento impone ugualmente un limite alla velocità massima con cui i dispositivi a giunzione possono essere utilizzati in commutazione. Quando un diodo porta una corrente elevata, è necessario un tempo superiore per rimuovere i portatori di carica e quindi il tempo di immagazzinamento cresce rispetto al valore assunto per le basse intensità di corrente.

Sebbene la descrizione che è stata data si riferisca ai diodi a giunzione, effetti di immagazzinamento di portatori di carica sono presenti in tutti i dispositivi a giunzione p-n (transitori, tiristori, triac, ecc.) quando essi passano dallo stato di conduzione a quello di interdizione.

#### 1.7 Diodi a barriera Schottky

Un diodo Schottky è un dispositivo raddrizzatore a giunzione metallosemiconduttore. Il materiale semiconduttore è solitamente di tipo n, ma possono essere usati anche materiali semiconduttori di tipo p. I diodi Schottky non presentano effetti di immagazzinamento di portatori di carica e hanno perciò un tempo di immagazzinamento nullo: questo per il diverso meccanismo di funzionamento dei diodi Schottky rispetto ai dispositivi a giunzione p-n.

Per ridurre il tempo totale di accensione o spegnimento di alcuni tipi di porte logiche, vengono inseriti nei loro circuiti alcuni diodi Schottky.

#### 1.8 Transistori bipolari a giunzione

Il nome transistore è una contrazione di **TRAN**sfer re**SISTOR**, che gli inventori idearono per descrivere il suo funzionamento. Il termine "bipolare" proviene dal fatto che entrambe le polarità dei portatori di carica, cioè buche ed elettroni, sono coinvolte nel trasporto di corrente attraverso il dispositivo.

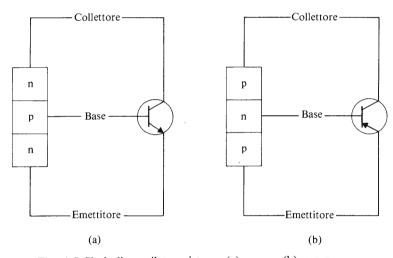

Il transistore bipolare è un dispositivo semiconduttore a 3 strati ottenuto da una fetta sottile (*chip*) di materiale semiconduttore, di solito silicio o germanio. Le tre regioni sono note come **emettitore**, base e collettore (Fig. 1.5).

Fig. 1.5 Simboli per il transistore: (a) n-p-n; (b) p-n-p.

Il simbolo del transistore è disegnato in modo tale da fornire informazioni sul transistore stesso: una freccia è disegnata sempre sull'elettrodo emettitore, e indica il verso della corrente convenzionale (flusso di buche); in tal modo, se la freccia si allontana dalla base, la base è di tipo p; se la freccia si dirige verso la base, la base è di tipo n. L'emettitore deve il suo nome al fatto che da esso provengono i portatori di carica; il collettore invece è così chiamato perché la maggioranza dei portatori di carica che lasciano l'emettitore sono ivi raccolti. La sottile regione della base fornisce i mezzi elettrici per controllare il flusso di corrente attraverso il transistore; deve il suo nome al fatto che nei primi transistori era la pesante base fisica che faceva da supporto al transistore.

I due tipi principali di transistori a giunzione sono il tipo n-p-n e quello p-n-p (Fig. 1.5). Le dimensioni reali di un transistore sono molto ridotte; ad esempio un tipo di transistore ha una superficie di:

$$7 \times 30 \ \mu\text{m}^2 \ (1 \ \mu\text{m} = 10^{-6} \ \text{m})$$

Entrambi i tipi di transistori sono in uso e ciascuno di essi è costituito da un unico chip di materiale semiconduttore. Di seguito viene descritto un metodo di fabbricazione.

Nell'utilizzazione pratica, le sorgenti di tensione applicate a un transistore bipolare sono due: una alimenta il circuito di ingresso e l'altra il circuito di uscita, ed entrambe hanno un collegamento elettrico in comune. In un circuito reale le due tensioni menzionate sono fornite da uno stesso generatore.

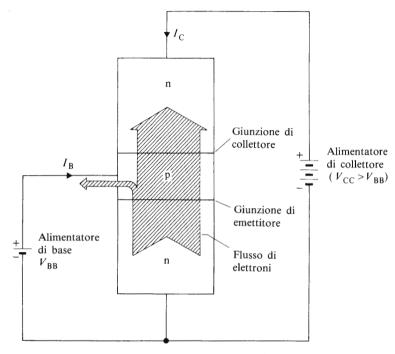

Il tipo di elettrodo del transistore che è collegato al punto comune sopracitato caratterizza il circuito; abbiamo così il circuito a emettitore comune, il circuito a base comune e il circuito a collettore comune. Il circuito a emettitore comune è il più usato e una sua versione semplificata è mostrata in Fig. 1.6.

Quando tale circuito è usato come elemento logico di commutazione, la corrente di base  $I_B$  ha un valore molto elevato (elevato, s'intende, in termini elettronici) o è nulla. Consideriamo in primo luogo la condizione in cui  $I_B$  ha un valore elevato, cioè quando il valore della tensione dell'alimentatore di base  $V_{BB}$  polarizza direttamente la giunzione p-n emettitore-base.

Per studiare più in dettaglio il funzionamento del transistore è necessario sapere qualcosa di più sui livelli di drogaggio delle regioni al suo interno. Quando si costituiscono i transistori, si fa sempre in modo che la regione dell'emettitore sia molto drogata, cosicché possegga un'eccedenza di portatori mobili di carica; l'emettitore della Fig. 1.6 è di tipo n, cioè ha un eccesso di elettroni mobili. Inoltre, la base è drogata molto lievemente e dispone solo di pochi portatori mobili di carica (cioè di buche nella base di tipo p); difatti la base è drogata così poco da essere praticamente una regione di tipo i; essa è inoltre molto sottile (il suo spessore è dell'ordine della lunghezza d'onda della luce visibile).

Quando la giunzione emettitore-base è polarizzata direttamente, i portatori mobili di carica si muovono attraverso la giunzione stessa in entrambe le direzioni, ma il grande numero di elettroni emessi dall'emettitore verso la base è assai superiore a quello delle buche presenti nella base. Di conseguenza un'elevata concentrazione di elettroni (portatori di minoranza nella base di tipo p) viene a costituirsi nella base stessa. Le

Fig. 1.6 - Collegamento con emettitore comune

buche mobili nella base che si combinano con alcuni di questi elettroni danno origine a un flusso di corrente  $(I_B)$  nel circuito di base esterno. Il valore del potenziale del collettore  $(V_{CC})$  è normalmente superiore a quello del potenziale di base, cosicché la giunzione del collettore è polarizzata inversamente e un flusso di corrente normale in "direzione positiva" (cioè un flusso di buche) non può aver luogo tra di essi. Tuttavia la regione di base di tipo p ora contiene un'elevata concentrazione di elettroni (portatori di minoranza) ed essi vengono attratti verso il collettore dal potenziale positivo dell'alimentazione del collettore stesso. In pratica si trova che il  $98 \div 99,9\%$  degli elettroni che lasciano l'emettitore arrivano al collettore, e che molto pochi fluiscono attraverso il circuito di base esterno.

Il variare della corrente di base ha l'effetto di produrre una variazione quasi proporzionale nella corrente del collettore, e ciò viene usato per controllare il flusso di corrente attraverso il transistore. Quando la corrente di base è nulla, anche la corrente del collettore si annulla.

Così, il percorso tra il collettore e l'emettitore di un transistore può essere usato come un **interruttore elettronico** nel seguente modo: quando la corrente di base è elevata (tra i 10 e i 100  $\mu$ A), la corrente del collettore è pure elevata e l'interruttore è ON, cioè chiuso; la resistenza del cammino tra il collettore e l'emettitore è bassa (circa 20  $\Omega$ ). Quando la corrente di base è nulla, la corrente del collettore è pure nulla e l'interruttore è OFF, cioè aperto. Una semplice applicazione di questo genere di interruttori elettronici è descritta nel capitolo 3.

Nella televisione e nel campo delle radio ed audiofrequenze la corrente del transistore viene variata con continuità secondo l'intensità del segnale in arrivo, mentre nei circuiti logici la corrente può essere solo nello stato ON o nello stato OFF.

#### 1.9 Transistori a effetto di campo (FET)

La variabile di controllo di un transistore a effetto di campo è una tensione che crea un campo elettrico all'interno del transistore stesso. In generale, i FET possono essere divisi in due grandi famiglie: quella dei FET con il gate isolato o FET a Metallo-Ossido-Semiconduttore (JGFET o MOSFET) e quella dei FET con il gate a giunzione (JFET o JUGFET). I JUGFET hanno poche applicazioni nel campo dell'elettronica digitale e rimandiamo perciò il lettore al volume di Noel M. Morris, Elementi di elettronica teorica e pratica, Hoepli, per ulteriori informazioni su di essi.

#### 1.10 I MOSFET

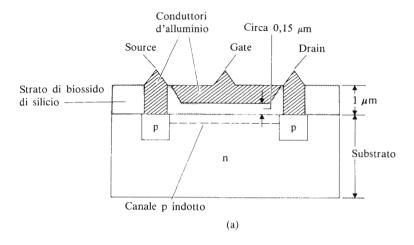

La sezione di un MOSFET è mostrata in Fig. 1.7(a). Il dispositivo in figura è formato da un substrato di materiale di tipo n; lo spessore del substrato è generalmente di 200  $\mu$ m. Il dispositivo ha tre elettrodi detti **source** (pronuncia s\overline{o}s), che è la sorgente dei portatori di carica immessi rispettivamente nel FET, **drain** (pronuncia dréin), dove i portatori di carica sono "scaricati" dal FET, e **gate** (pronuncia ghéit), che è l'elettrodo utilizzato per controllare il flusso di corrente attraverso il FET. I collegamenti tra il circuito esterno e gli elettrodi source e drain sono stabiliti mediante conduttori di alluminio che passano attraverso uno strato isolante di biossido di silicio (silice). Gli elettrodi source e drain sono materiali semiconduttori di tipo p che sono diffusi nel substrato di tipo n. Il gate è uno strato di alluminio isolato dal substrato tramite un sottilissimo velo di biossido di silicio; lo spessore di questo isolante è equivalente a 2 sole lunghezze d'onda della radiazione rossa!

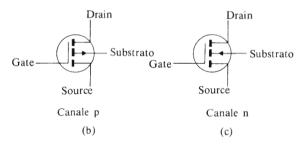

Fig. 1.7 (a) Sezione di un MOSFET a canale p. (b) Simbolo di un MOSFET a canale p. (c) Simbolo di un MOSFET a canale n

I lettori noteranno nella Fig. 1.7(a) che la zona tra il gate e il canale è formata di **M**etallo-**O**ssido-**S**emiconduttore, dalle cui iniziali deriva il nome MOSFET. Inoltre, dato che il gate è isolato dal substrato, questi transistori sono detti anche Insulated-Gate FET o IGFET.

Il dispositivo illustrato in Fig. 1.7(a) è noto come MOSFET a canale p, cosiddetto perché il flusso di corrente tra il source e il drain è dovuto al movimento di buche (cariche positive); in questo caso il source è collegato al polo positivo dell'alimentatore (sorgente perciò di buche) e il drain al polo negativo.

Quando la tensione tra il gate e il source è zero (cioè quando essi sono collegati tra di loro) la giunzione p-n tra il drain e il substrato è polarizzata inversamente (si ricordi che la regione del drain di tipo p è collegata

col polo negativo del generatore) e impedisce in questo modo il flusso di corrente. Di conseguenza, quando la tensione di gate è zero la corrente del drain è zero. Considerando il percorso tra il drain e il source come il contatto di un interruttore elettronico, l'interruttore è aperto o OFF quando la tensione di gate è zero.

Il substrato del MOSFET è molto poco drogato e, sebbene venga descritto come un materiale di tipo n, possiede un numero esiguo di elettroni mobili. Oltre a questi elettroni contiene una quantità addizionale di elettroni e buche generati da effetti termici secondo il processo descritto nel paragrafo 1.1. Se fosse possibile provocare l'accumulo in un unico punto delle buche generate termicamente, si avrebbe la conversione di una piccola zona del substrato lievemente drogato di tipo n in una zona di tipo p. Ciò può essere provocato applicando un potenziale negativo al gate (negativo rispetto al source); tale potenziale attrae le buche del substrato nella superficie inferiore dello strato di biossido di silicio appena sotto il gate. Per un valore del potenziale di gate noto come potenziale di soglia, un numero sufficiente di buche si raccoglie a formare un canale di conduzione tra il source e il drain: questo fenomeno crea il canale di tipo p della Fig. 1.7(a). Il valore del potenziale di soglia, detto valore di soglia  $V_T$ , per un dispositivo a canale di tipo p oscilla tra -2 V e5 V. Portando il potenziale di gate a valori più negativi del valore di soglia, aumenta la conduttività del canale indotto e si determina una corrente di drain di maggiore intensità. Perciò l'interruttore elettronico è acceso quando viene applicato un potenziale di gate superiore al valore di soglia (in valore assoluto).

Un dispositivo di questo tipo è conosciuto come **FET a riempimento**, dato che aumentando (sempre in valore assoluto) il potenziale di gate aumenta la corrente di drain che provoca il riempimento del canale.

I simboli per il circuito della Fig. 1.7 forniscono informazioni sui MOSFET con il seguente schema: la linea tratteggiata tra il source e il drain implica che la corrente di drain è zero (il canale è interrotto) quando il potenziale di gate è zero; la distanza tra il gate e il canale indica che si tratta di un MOSFET; la direzione della freccia che parte dalla porzione centrale del canale indica il tipo di materiale del canale stesso: se la freccia è diretta dal canale verso il substrato (Fig. 1.7b) il canale è di tipo p, poiché la direzione della freccia è la stessa di quella associata a un diodo convenzionale di tipo p-n; se la freccia si dirige verso il canale (Fig. 1.7c), allora il dispositivo è un MOSFET a canale n.

Vengono prodotti sia MOSFET a canale n, sia a canale p. I dispositivi a canale n operano ovviamente con il drain collegato al polo positivo del generatore e con un potenziale di gate positivo.

#### 1.11 Precauzioni nel maneggiare i MOSFET

Dato che lo strato di biossido di silicio tra il gate e il substrato è molto sottile, esso può venir permanentemente danneggiato dall'applicazione di tensioni relativamente basse nella regione del gate; il potenziale di rottura di questo strato di biossido di silicio varia fra 30 e 100 V. Tensioni di questo ordine di grandezza possono venire applicate semplicemente da chiunque maneggi il dispositivo; non è infrequente che una persona accumuli un potenziale statico in eccesso di 20 kV! I potenziali statici vengono generati dall'attrito tra la pelle e i vestiti o altri oggetti esterni. Per evitare possibili danni nel maneggiare e nel collaudare il dispositivo bisogna prendere alcune precauzioni:

- Per evitare l'accumularsi di carica statica durante il trasporto e il contatto con le mani precedente l'uso effettivo del dispositivo, i suoi terminali dovrebbero essere in contatto con un materiale conduttore (per esempio una plastica conduttrice).

- Tutti gli strumenti usati nel lavoro di montaggio dovrebbero essere collegati a terra; tra essi i saldatori e le parti metalliche dei supporti e degli strumenti.

- 3. I dispositivi MOS non dovrebbero essere inseriti o rimossi da circuiti quando è applicata una tensione esterna. Questo può provocare picchi di tensione nel circuito.

- 4. Quando i dispositivi MOS sono in uso, i terminali inutilizzati dovrebbero essere collegati a terra o alla linea di alimentazione, secondo ciò che sia conveniente per il tipo di porta logica in considerazione.

- 5. Non si dovrebbero applicare segnali alle linee di ingresso delle porte logiche mentre la tensione di alimentazione del dispositivo è nulla.

- Le suddette precauzioni dovrebbero venir osservate nel collegamento con piastre che non siano inserite in un sistema in cui sono già applicate le corrette tensioni.

Altri metodi di protezione si possono fornire per l'impiego nel luogo dove i dispositivi MOS vengono montati sui circuiti. Essi includono appoggiapiedi conduttori sotto i tavoli di lavoro degli operatori, coprisgabelli conduttori, pavimenti conduttori, moquette conduttrici e ricopertura dei banchi pure conduttrice.

E' spesso consigliabile per gli operatori l'uso di un cinturino da polso messo a terra mentre lavorano con i dispositivi MOS, ma esso non deve essere considerato sufficiente come unico mezzo di protezione, anche perché è possibile dimenticarsi di collegarlo al circuito. Inoltre un cinturino di questo tipo potrebbe limitare i movimenti dell'operatore.

Un ulteriore pericolo può sorgere nel trattare gli elementi MOS se il dispositivo assemblato viene pulito con uno spray solvente dopo l'operazione di saldatura. La pulizia a spray può generare un'alta differenza di potenziale elettrico; bisogna consultare in proposito un esperto di montaggio.

Inoltre, è consigliabile per qualsiasi persona che debba maneggiare i dispositivi MOS portare una tuta fatta di materiale antistatico, anziché di nylon o di altra fibra sintetica.

#### 1.12 Circuiti integrati monolitici (IC)

Dato che il silicio possiede caratteristiche che meglio si adattano ai processi di costruzione dei circuiti integrati, tutti i circuiti integrati monolitici sono realizzati con questa sostanza. La parola "monolitico" implica semplicemente che i circuiti integrati sono realizzati da un monocristallo. I processi fondamentali di produzione sono desritti di seguito.

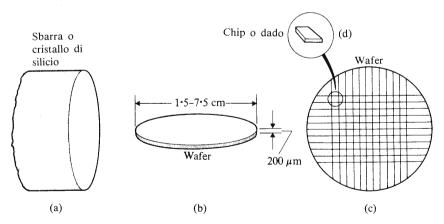

Innanzitutto, la silice (sabbia comune) è ridotta a silicio puro, dal quale si ricava un cristallo cilindrico avente le dimensioni tipiche di 30 cm di lunghezza e 7,5 cm di diametro. Il cristallo di silicio viene quindi tagliato da una sega diamantata in un gran numero di *wafer* cilindrici che, dopo la pulitura, hanno uno spessore di circa 200  $\mu$ m, come illustrato nella Fig. 1.8(a) e (b). Dopo che il wafer di silicio è stato sottoposto a una serie di processi descritti in seguito, esso contiene un gran numero di singoli circuiti. Le dimensioni fisiche di questi circuiti possono essere anche molto piccole; in alcuni casi essi sono dei quadrati con il la-

Fig. 1.8 Procedimenti per la costruzione di un circuito integrato monolitico

to lungo una frazione di millimetro. Per separare questi circuiti l'uno dall'altro, il wafer è diviso in tanti piccoli *chips* o *dadi* con procedimenti simili a quelli di taglio del vetro. Ciò è illustrato nei diagrammi (c) e (d) della Fig. 1.8. Ogni chip contiene un circuito completo.

Il chip viene quindi montato su un supporto e, dopo il completamento delle connessioni tra il circuito integrato e i terminali esterni, viene incapsulato per evitare contaminazioni dall'atmosfera circostante.

Il tipo di circuito integrato prodotto col metodo appena descritto è noto come circuito integrato *planare epitassiale* (epitassiale deriva dal greco e significa "costruito sopra"; l'espressione planare epitassiale significa che il circuito integrato è montato su una superficie piana).

#### 1.13 Costruzione di un circuito integrato bipolare

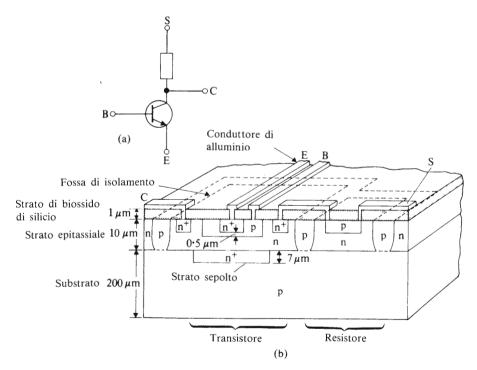

Considereremo ora come viene costruito in forma integrata il circuito della Fig. 1.9(a); la rete mostrata potrebbe far parte di un circuito inter-

Fig. 1.9 Costruzione di un tipico circuito integrato monolitico

ruttore. Una volta completato, il circuito integrato appare come in Fig. 1.9(b), essendo le dimensioni totali del transistore di circa  $100 \ \mu m^2$ . I passaggi intermedi del processo di costruzione sono riassunti di seguito.

#### Lo strato sepolto n<sup>+</sup>

Il chip di silicio costruito nel processo iniziale è usato come *substrato* sul quale viene assemblato il circuito completo. La resistività del materiale del substrato è abbastanza elevata e ne deriverebbe che qualsiasi transistore costruito al suo interno sarebbe inutilizzabile come dispositivo interruttore. Per ovviare a questo difetto si diffonde nel substrato uno "strato sepolto" di tipo n<sup>+</sup> di materiale semiconduttore con un'elevata conduttività, in un punto sul chip che si trova direttamente sotto la zona dove il transistore si verrà a trovare alla fine. Un materiale di tipo n<sup>+</sup> è un qualsiasi materiale con un valore di conduttività superiore a quello di materiali convenzionali di tipo n. Il processo di diffusione è qui descritto sotto i titoli di *Crescita dell'ossido e mascheratura fotografica* e *Diffusione* ed è generalmente simile al processo di diffusione usato nella costruzione delle altre parti del circuito. Lo strato "sepolto" è così chiamato perché è effettivamente sepolto sotto la superficie del circuito.

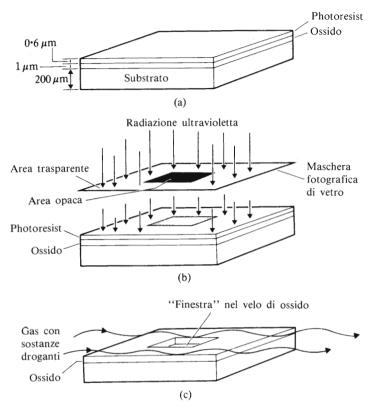

#### Crescita dell'ossido e mascheratura fotografica

Dopo la pulitura e l'esame a vista, la superficie superiore del substrato è ossidata mediante passaggio di vapore su di essa; lo strato di ossido prodotto da questo processo ha uno spessore di circa 1  $\mu$ m. La superficie superiore dell'ossido è ricoperta con un materiale fotosensibile noto come *photoresist*, come mostrato nella Fig. 1.10(a). Il photoresist è esposto a radiazioni ultraviolette attraverso una maschera fotografica (Fig. 1.10b) e le aree esposte del photoresist si induriscono. Le aree non esposte, coperte dalle aree opache della maschera, rimangono "soffici" e vengono dissolte con un solvente, lasciando un'apertura nel photoresist. La fetta è quindi attaccata chimicamente da un acido per rimuovere lo strato di ossido corrispondente all'apertura, lasciando così una "finestra" nella superficie superiore del substrato. Il photoresist residuo è poi rimosso mediante l'uso di altri solventi, dopo di che la fetta viene sciacquata ed essiccata.

Fig. 1.10 Fabbricazione dello strato sepolto n<sup>+</sup>

#### Diffusione

Nello stadio successivo della fabbricazione, la fetta viene fatta passare attraverso un forno di diffusione, dove viene scaldata a una temperatura di circa  $1200^{\circ}$ C e su di essa passano gas contenenti appropriate sostanze droganti (Fig. 1.10c). La sostanza drogante nel gas fa sì che l'area esposta del substrato di tipo p si converta in un materiale di tipo n<sup>+</sup>. Lo strato sepolto, diffuso in questo modo attraverso la finestra nello strato di ossido, penetra fino a una profondità di circa  $7~\mu m$ . Lo strato di ossido viene quindi asportato, lasciando il substrato di tipo p a contatto con lo strato sepolto n<sup>+</sup> sulla sua superficie.

#### Strato epitassiale

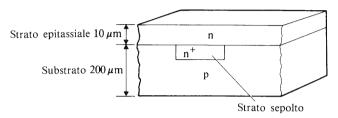

La fetta viene poi riscaldata un'altra volta in un forno e soggetta a gas che provocano la "crescita" di uno strato epitassiale uniforme su tutta la superficie (Fig. 1.11). In questo strato epitassiale, spesso  $10 \mu m$ , viene costruito l'intero circuito integrato.

Fig. 1.11 Sezione trasversale di wafer dopo la formazione dello strato epitassiale

#### Componenti di circuito

Per isolare i componenti all'interno del circuito l'uno dall'altro, è necessario formare fosse di isolamento attorno alle zone in cui i componenti stessi verranno a formarsi. Con un processo di mascheratura, attacco chimico e diffusione simili a quelli sopra descritti, vengono diffuse le fosse di isolamento di tipo p all'interno dello strato epitassiale (Fig. 1.9b). La fossa di isolamento fornisce un collegamento tra la superficie del circuito integrato e il substrato e isola elettricamente l'area che essa circonda.

Vengono poi aperte finestre nello strato di ossido per potervi introdurre, mediante diffusione, la base di tipo p e il resistore. Il successivo processo di diffusione permette non solo l'introduzione dell'emettitore del transistore, ma anche delle due regioni n<sup>+</sup> nel collettore. Queste due regioni devono permettere sia una connessione con la regione del collettore vero e proprio che un'interconnessione tra il collettore e il resistore.

#### Completamento del circuito integrato

Uno strato di alluminio spesso circa  $1,5~\mu m$  viene fatto evaporare sull'intera superficie del circuito e le regioni che non servono per le connessioni elettriche vengono rimosse tramite un processo di attacco chimico. Vengono quindi realizzate le connessioni tra l'alluminio rimasto e i piedini esterni del circuito integrato.

La descrizione appena riportata è una semplificazione dei processi adottati e, come il lettore noterà, anche la Fig. 1.9(b) è stata schematizzata. In totale, circa 80-100 singoli stadi sono necessari nella costruzione di un circuito integrato bipolare, alcuni dei quali richiedono poche ore, altri alcune settimane.

#### 1.14 Costruzione dei circuiti integrati MOS

La sezione trasversale di un MOSFET a canale p costruito in forma integrata è riportata nella Fig. 1.7(a) e mostra le caratteristiche essenziali del dispositivo. Quando viene confrontata con il circuito bipolare integrato della Fig. 1.9, diventa subito evidente che il dispositivo MOS è più semplice da costruire. Inoltre richiede sul chip semiconduttore una superficie minore di quella di un transistore bipolare. Di conseguenza è possibile con gli elementi costitutivi di un MOS produrre un circuito più complesso su una data superficie del chip o produrre lo stesso circuito ad un costo inferiore che con gli elementi bipolari. In tal modo, le funzioni logiche nella maggior parte delle macchine calcolatrici elettroniche sono fornite da dispositivi MOS in forma di circuiti integrati.

#### 1.15 Impaccamento di circuiti integrati

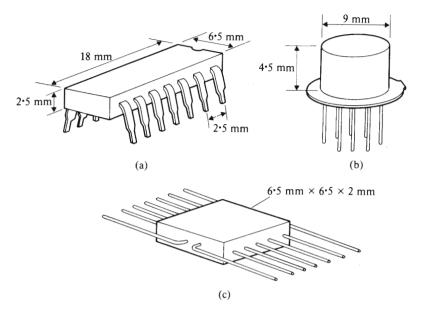

Le tre forme più comuni di impaccamento di circuiti integrati sono mostrate nella Fig. 1.12. La forma più consueta è il DIP (dual-in-line pack), di plastica incapsulata (Fig. 1.12a) con 14 piedini in doppia fila, sette per lato, ciascun paio allineato con gli altri a una distanza di circa 2,5 mm per permettere al circuito integrato di essere inserito direttamente su circuiti stampati standard. Il *canister* o *can* (Fig. 1.12b) porta il circuito integrato in un contenitore a forma di barattolo ermeticamente sigillato. Il *flatback* (Fig. 1.12c), spesso in ceramica, è pure sigillato ermeticamente.

#### 1.16 Circuiti MSI e LSI

I termini circuito a scala media di integrazione (MSI = medium-scale integrated circuit) e circuito a larga scala di integrazione (LSI = large scale integrated circuit) sono usati generalmente per descrivere alcuni tipi di circuiti logici complessi. Si riferiscono al numero di porte logiche complete contenute in un integrato e, sebbene un po' imprecisamente, possono essere interpretati come segue:

Fig. 1.12 Impaccamento dei circuiti integrati

- a) i circuiti MSI contengono dalle 10 alle 100 porte logiche;

- b) i circuiti LSI contengono più di 100 porte logiche.

I circuiti integrati usati nelle calcolatrici elettroniche sono circuiti LSI.

## Porte logiche di base

#### 2.1 Porte logiche

Un sistema logico è un sistema che funziona sempre in una maniera predeterminata, cosicché, dato un insieme di condizioni, si viene a produrre sempre lo stesso tipo di risposta.

Le regole basilari sono abbastanza facili da capire e da applicare: la funzione di una **porta logica** è quella di controllare il flusso di **informazioni** o di **dati** attraverso il sistema; il nome "porta" fu coniato in base al fatto che un dispositivo logico può presentarsi **aperto** al flusso di dati attraverso di esso, o **chiuso** rispetto allo stesso.

Bisogna sottolineare che il livello di potenza associato ad un segnale logico è molto basso (generalmente di pochi microwatt), ma il livello di potenza necessario per far funzionare la porta logica può essere relativamente elevato. Un'analogia tra i livelli di potenza che sono coinvolti in un'auto può aiutarci a illustrare la situazione. La potenza effettiva del segnale richiesta per far avanzare l'auto è semplicemente quella richiesta per inserire la marcia avanti (azione equivalente al nostro segnale logico), ma la potenza che il motore deve sviluppare per provocare il movimento in avanti dell'auto (equivale alla potenza richiesta per azionare la parte logica) può essere molto elevata. E'opportuno conoscere qualcosa sulle potenze in gioco in un sistema logico ma l'interesse dei lettori è diretto principalmente verso il controllo del flusso dei segnali logici attraverso il sistema.

Il funzionamento di ciascuna porta logica deve conformarsi a regole strettamente definite e le principali porte logiche sono denominate AND, OR e NOT; una descrizione delle versioni di queste porte è data in questo capitolo. Altre porte, note come NAND e NOR, sono descritte più avanti.

# 2.2 Livelli di segnali logici

Un sistema logico è un sistema che fornisce una soluzione definita per tutte le possibili condizioni in cui può trovarsi il circuito. Questo significa che l'uscita può sempre venir espressa nella forma di una risposta "sì" o "no" — la risposta non può mai essere "forse": abbiamo a che fare con un sistema a due livelli o binario, cosicché il potenziale di uscita da una porta logica può assumere solo 2 valori, per esempio +5 V o 0 V. Usando una notazione nota come logica positiva, il segnale di +5 V rappresenta la condizione di "sì" o "vero". In questa notazione un segnale "vero" è rappresentato dal cosiddetto "1" logico e un segnale "falso" dal cosiddetto "0" logico.

Si può usare anche una notazione alternativa, nota come **logica negativa**; in essa il segnale 0 V rappresenta l'"1" logico o il segnale "vero", mentre il +5 V rappresenta lo "0" logico, cioè il segnale "falso".

Sebbene abbiamo menzionato soltanto i livelli di potenziale di +5 V e 0 V, ogni differenza di potenziale come +3 V e —12 V può essere utilizzata in pratica. Nell'esempio appena citato avremmo:

|                             | Esempio 1 | Esempio 2 |

|-----------------------------|-----------|-----------|

| (a) con logica positiva:    |           |           |

| il potenziale massimo è "1" | +5 V      | +3 V      |

| il potenziale minimo è "0"  | 0 V       | -12 V     |

| (b) con logica negativa:    |           |           |

| il potenziale minimo è "1"  | 0 V       | -12 V     |

| il potenziale massimo è "0" | + 5 V     | +3  V     |

Sebbene la notazione della logica positiva sia quella più usafa, la logica negativa è pure utilizzata in alcune famiglie logiche; si tratterà di questo più diffusamente nel paragrafo 2.9.

# 2.3 Un problema logico

Per illustrare il modo in cui operano i circuiti logici fondamentali, consideriamo il funzionamento di una ipotetica macchina per inscatolare giocattoli.

I giocattoli da inscatolare sono camion o automobiline; gli uni e le altre vengono trasportati su nastri scorrevoli indipendenti; se la scorta di scatole sta per esaurirsi, la macchina deve generare un segnale di allarme da trasmettere ai magazzini per indicare la penuria di scatole. La mac-

china dovrebbe continuare a operare finché c'è una scatola disponibile e se c'è un giocattolo da mettere nella scatola.

I paragrafi da 2.4 a 2.7 considerano il funzionamento dei circuiti che possono essere utilizzati per creare i segnali logici appropriati.

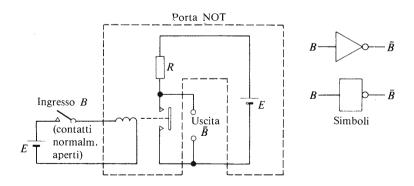

# 2.4 La porta NOT

Descrivendo i segnali logici, abbiamo visto che i segnali (ovvero le tensioni) in un sistema logico hanno solo due livelli possibili, e cioè quello corrispondente all'"1" logico e quello corrispondente allo "0" logico: ciò significa che, se l'uscita di una porta è "1" allora NOT è "0" e viceversa (in inglese NOT = non). Una porta NOT è una porta che fornisce uno "0" all'uscita quando il suo ingresso è "1", e un "1" all'uscita quando il suo ingresso è "0", cioè si dice che inverte o complementa il segnale logico che si presenta all'ingresso.

La Fig. 2.1 mostra un circuito NOT elementare che usa un relè. Una tensione viene applicata dall'interruttore B all'ingresso della porta (la bobina del relè) e l'uscita è prelevata attraverso i due contatti del relè. La resistenza R ha la funzione di limitare la corrente. Assumiamo che il circuito operi con la notazione della logica positiva, cioè che quando le tensioni di ingresso o di uscita sono +E (positive), venga descritto con l'"l' logico e quando una tensione è zero venga descritta con "0" logico.

Nella Fig. 2.1 l'interruttore è aperto, B=0 e la bobina del relè è smagnetizzata; i contatti del relè sono perciò aperti. In questo caso la corrente attraverso R e la caduta di potenziale attraverso di essa sono zero. La tensione di uscita è perciò +E o l'"1" logico. Cioè il segnale

Fig. 2.1 Una porta logica NOT a relè

#### PORTE LOGICHE DI BASE

di uscita è il complemento logico del segnale d'entrata (ingresso = 0, uscita = 1).

Se l'interruttore è chiuso, il segnale B=1 e la bobina del relè è magnetizzata; il contatto del relè è chiuso e la tensione di uscita è zero, ovvero lo "0" logico. Ancora, il segnale di uscita è il complemento logico del segnale d'ingresso (ingresso = 1, uscita = 0).

In pratica, il circuito a relè della Fig. 2.1 viene sostituito con un circuito semiconduttore (vedi capitolo 3). I simboli mostrati in figura possono essere utilizzati sia per il circuito a relè che per il suo equivalente a semiconduttore; questa osservazione è valida anche per tutte le altre porte logiche descritte nel capitolo.

Il funzionamento del circuito è riassunto in quella che viene chiamata la tabella della verità della porta (Tabella 2.1): essa è semplicemente un

| Ingresso | Uscita         |

|----------|----------------|

| В        | $\overline{B}$ |

| 0        | 1              |

| 1        | 0              |

Tabella 2.1 Tabella della verità per una porta NOT

metodo tabulare per mostrare le condizioni logiche di uscita del circuito per tutte le condizioni possibili di ingresso. Dato che alla porta NOT è applicato un solo segnale logico d'ingresso che può assumere una delle due condizioni (cioè "0" o "1"), ci sono solo due righe nella tabella della verità. L'uscita è espressa nella forma

Uscita = NOT

$$B = \overline{B}$$

La lineetta è messa sopra B per significare l'inversione logica. ( $\bar{B}$  si legge "B negato").

Consideriamo ora l'uso della porta NOT nel problema del paragrafo 2.3. Una condizione stabilisce che quando la scorta di scatole sta per esaurirsi, è necessario informare i magazzini affinché forniscano le scatole mancanti. Se le scatole sono impilate in una tramoggia e l'interruttore B è messo in qualche modo su di essa, quando la tramoggia contiene scatole l'uscita di B è l''1' logico. L'uscita della porta NOT corrispondente al segnale di ingresso B può essere collegata a una lampada

d'allarme nei magazzini, la quale, quando si accende, illumina la scritta carenza di scatole. Chiaramente, quando ci sono scatole nella tramoggia allora B=1 e  $\overline{B}=0$ , quindi la lampada d'allarme è spenta. Quando la scorta di scatole si sta esaurendo, l'interruttore B si apre (B=0),  $\overline{B}$  diventa 1 e la lampada carenza di scatole si accende.

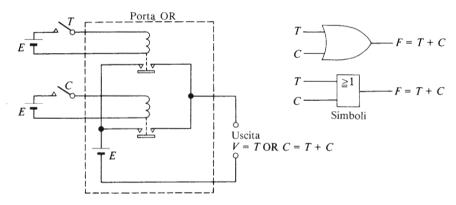

# 2.5 La porta OR

Nella descrizione del sistema abbiamo detto che i giocattoli possono essere inscatolati se è presente un camion OR un'automobilina (in inglese OR = 0, oppure). La presenza dei camion può essere indicata da un interruttore T e quella delle automobiline da un interruttore C. Se l'uscita della porta che decide se è presente almeno uno dei due tipi di veicoli è indicata con V, allora diciamo che

$$V = T$$

OR  $C = T + C$

dove il simbolo "più" (+) è usato per rappresentare la funzione logica OR. Il lettore non deve confondere il simbolo logico "+" con il simbolo di addizione aritmetica, poiché questi due simboli differiscono in un punto importante di cui parleremo più avanti.

In questo caso la porta ha due ingressi (da T e da C); quando T ha il valore "0", C può avere sia il valore "0" sia il valore "1". Anche quando T ha il valore "1", C può assumere il valore "0" o il valore "1". Ci sono perciò quattro combinazioni possibili delle due variabili; esse vengono elencate nella Tabella 2.2, che mostra inoltre l'uscita logica della porta OR per tutte le combinazioni possibili degli ingressi. La tabella della verità indica che quando T=0 e C=0, non ci sono veicoli

Tabella 2.2 Tabella della verità per una porta OR a 2 ingressi

| Ingr | essi | Uscita               |

|------|------|----------------------|

| T    | С    | V = T OR $C = T + C$ |

| 0    | 0    | 0                    |

| 0    | 1    | 1                    |

| 1    | 0    | 1                    |

| 1    | 1    | 1                    |

|      |      |                      |

#### PORTE LOGICHE DI BASE

presenti e V=0. Quando c'è un'automobilina disponibile, ma non c'è un camion (T=0, C=1), possiamo riconoscere la presenza di un veicolo (V=1); quando c'è un camion disponibile, ma non c'è un'automobilina (T=1, C=0), di nuovo V=1. Anche quando sono disponibili sia un camion che un'automobilina, è di nuovo V=1. Così l'affermazione 1 OR 1=1+1=1 è un'affermazione logica valida.

La tabella della verità della porta OR può essere riassunta come segue. L'uscita è l'"1" logico se almeno uno degli ingressi è l'"1" logico; l'uscita è lo "0" logico solo quando tutti gli ingressi sono lo "0" logico.

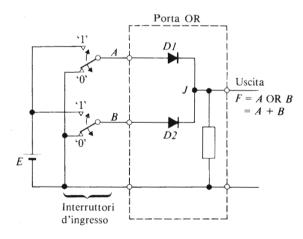

La Fig. 2.2 mostra una porta logica OR che contiene dei relè. I segnali di ingresso T e C sono ottenuti dagli interruttori nel modo esposto. Quando a entrambi gli ingressi T e C sono applicate tensioni nulle (T=0, C=0), entrambi i contatti del relè sono aperti e la tensione di uscita è 0 (V=0). Nel caso in cui una delle due bobine del relè (o anche entrambe) sia magnetizzata (quando T=1 OR C=1), il terminale di uscita è collegato al generatore interno della porta e V=1. Questo tipo di circuito perciò soddisfa la tabella della verità della porta OR.

Fig. 2.2 Una porta OR

Nel caso più generale possono esserci numerosi ingressi nella porta, ciascuno guidato da un sensore indipendente e ciascuno dei quali alimenta una bobina indipendente. Supponiamo che gli ingressi provengano dai sensori A, B, C, D, E e che l'uscita sia designata con il simbolo X, allora X = A OR B OR C OR D OR E = A + B + C + D + E

# 2.6 La porta AND

Nella macchina ipotetica descritta nel paragrafo 2.3, useremo una porta AND per far partire quella parte della macchina che mette un giocattolo nella sua scatola. Per inscatolare un giocattolo, la macchina deve simultaneamente avere a disposizione un veicolo (camion o automobilina) AND una scatola (in inglese AND = e). Se usiamo il simbolo S per rappresentare il segnale d'uscita della porta AND, allora si ha che:

$$S = V$$

AND  $B = V.B$

dove il punto (.) è usato per denotare la funzione logica AND. Il lettore si ricorderà che il segnale V è generato da una porta OR (vedi paragrafo 2.5) e che il segnale B è ottenuto da un interruttore messo sulla pila di scatole.

Ancora una volta abbiamo due segnali d'ingresso o **variabili**, che danno quattro combinazioni di V e di B, come riportato nella Tabella 2.3. Dato che un veicolo può essere messo in una scatola solo quando la macchina ha a disposizione un veicolo e una scatola simultaneamente, allora S=1 solo quando V=1 AND B=1 simultaneamente (ultima riga della tabella 2.3). Quando almeno uno tra B e V assume il valore logico "0", S=0 (prime tre righe della tabella 2.3) e la macchina rimane inoperosa.

Tabella 2.3 Tabella della verità per una porta AND con 2 segnali d'ingresso

| Ingi | ressi | Uscita              |

|------|-------|---------------------|

| V    | В     | S = V  AND  B = V.B |

| 0    | 0     | 0                   |

| 0    | 1     | 0                   |

| 1    | 0     | 0                   |

| 1    | 1     | 1                   |

La tabella della verità della porta logica AND può essere riassunta come segue. L'uscita è lo "0" logico se uno degli ingressi (o entrambi) è lo "0" logico; l'uscita è l'"1" logico solo quando tutti gli ingressi sono l'"1" logico.

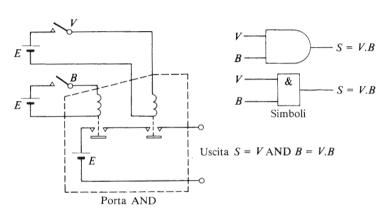

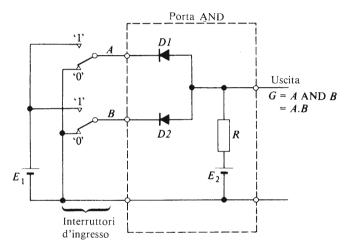

La Fig. 2.3 mostra una porta logica AND a relè. Il lettore noterà che, se V=0 oppure B=0, la corrispondente coppia di contatti del relè è aperta e S=0. Solo quando V=1 AND (e) B=1 simultaneamente, sono chiuse entrambe le coppie di due ingressi alla stessa porta, ciascuno da un sensore indipendente. In generale si possono avere molti ingressi alla porta logica, ognuno dei quali è azionato da un sensore indipendente. Supponiamo che gli ingressi vengano dai sensori Q, R, S, T e che l'uscita sia contrassegnata dal simbolo Z, allora si ha

# Z = Q AND R AND S AND T = Q.R.S.T

Fig. 2.3 Una porta AND

# 2.7 Il circuito completo di controllo

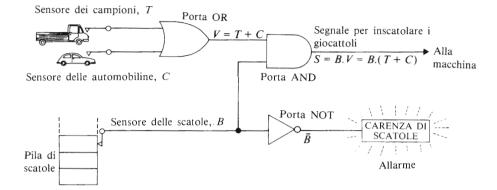

Un diagramma a blocchi del circuito logico che rappresenta il circuito di controllo della ipotetica macchina descritta nel paragrafo 2.3, è riportato nella Fig. 2.4.

Gli ingressi T e C sono ottenuti da sensori che rilevano la presenza dei corrispondenti tipi di veicolo, e il sensore B rileva la presenza o l'assenza di scatole per i giocattoli.

Il diagramma è tipico di un circuito logico nel senso che mostra solamente le connessioni necessarie per la trasmissione dei dati. Le altre connessioni, ad es. con i generatori, sebbene siano essenziali per il funzionamento del sistema, vengono omesse.

Poiché stiamo lavorando con uno schema logico a un livello relativa-

Fig. 2.4 Diagramma a blocchi del circuito di controllo per una macchina che inscatola giocattoli

mente elementare, il disegno della Fig. 2.4 mostra alcuni inconvenienti. Un problema abbastanza ovvio sorge quando un camion e un'automobilina arrivano simultaneamente; quale dei veicoli dovrà essere scelto? Questo e altri possibili difetti potranno essere corretti dal lettore stesso con l'aumentare delle sue informazioni ed esperienze sui sistemi logici.

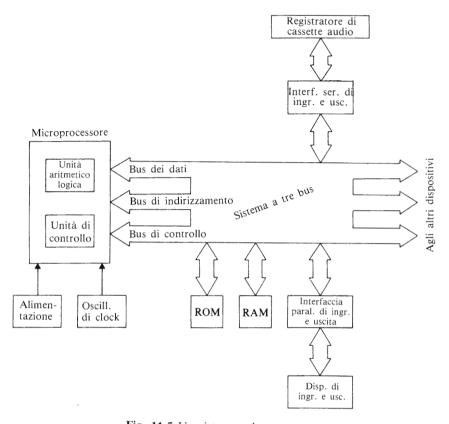

#### 2.8 Stesura di tabelle della verità